Nut_stm32f103c8侧信道分析

STM32F103C8是STMicroelectronics(意法半导体)公司推出的一款基于ARM Cortex-M3内核的微控制器芯片。该芯片因其高性能、低功耗以及丰富的外设资源在嵌入式系统中得到了广�泛的应用。

Nut_stm32f103c8开发板基于STM32F103C8芯片设计,适用于嵌入式芯片固件的侧信道分析研究和教学。本文以Nut_stm32f103c8为例,介绍如何使用Cracker-S1分析密码算法的功耗信息泄露。

STM32F103介绍

主要参数

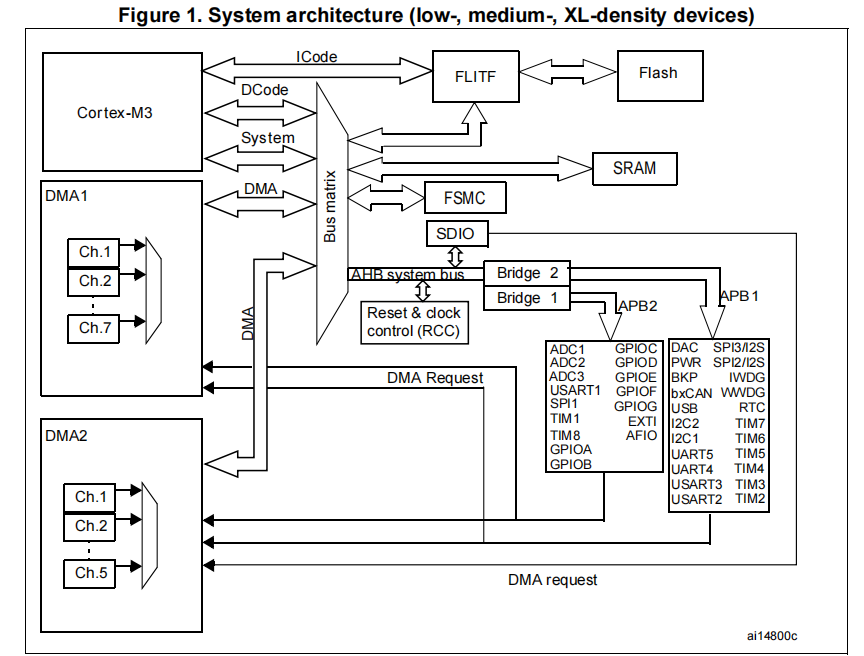

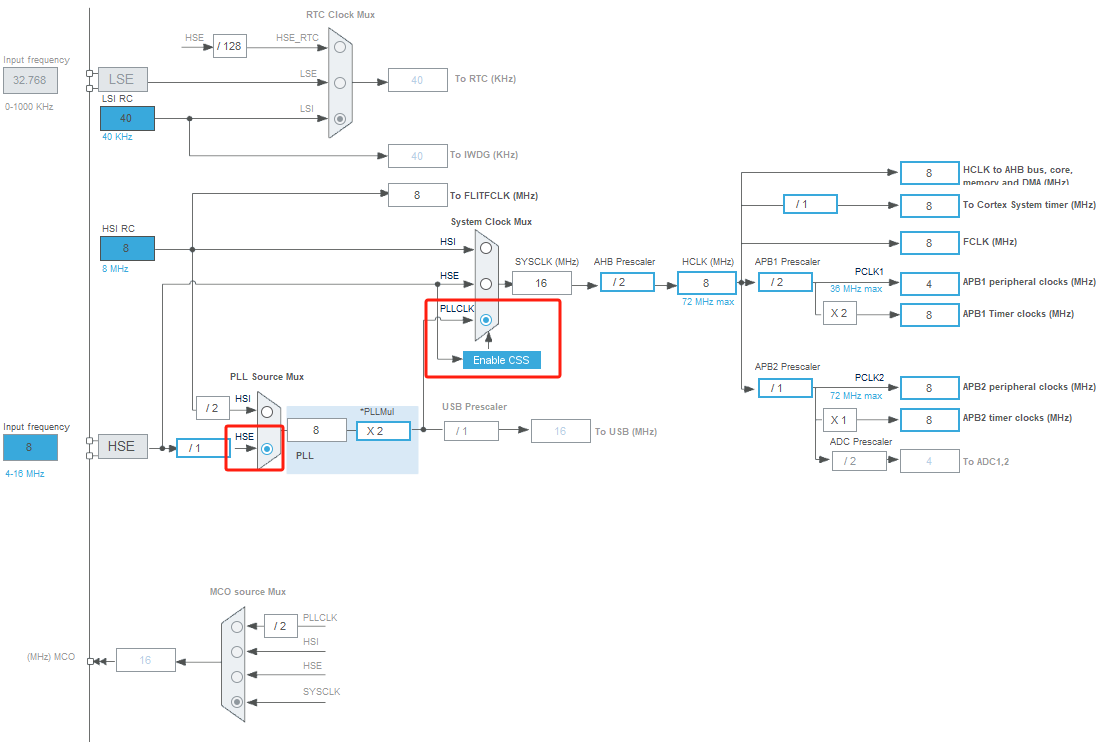

STM32F103C8芯片的架构如下图所示(RM0008)。

主要参数如下:

- 内核:采用ARM 32位的Cortex-M3处理器,主频最高可达72MHz,具有单周期乘法和硬件除法功能。

- 存储器:

- 最高512KB的闪存(Flash)用于存储程序代码。

- 最高64KB的SRAM用于数据存储。

- 时钟系统:

- 内部8MHz的RC振荡器。

- 支持外部4-16MHz的晶振。

- 可以通过PLL进行时钟倍频。

- 外设:

- 最多3个SPI接口、2个I2C接口、5个UART接口、2个USB接口(其中一个是全速USB)。

- 最多18个定时器,包括基本定时器、通用定时器以及高级定时器。

- 12位ADC转换器,最多可达16个通道。

- 12位DAC转换器,最多2个通道。

- CAN接口(部分型号)。

- 工作电压:2.0V至3.6V。

- 封装类型:LQFP、LFBGA、UFQFPN、WLCSP等�多种封装形式,提供不同的引脚数量以满足不同的设计需求。

- 低功耗模式:睡眠、停止和待机模式,有助于降低功耗,适用于电池供电的应用。

- 开发支持:ST提供了完善的软件开发环境,包括STM32CubeMX配置工具和HAL库,方便开发者进行程序设计和调试。

STM32F103系列因其性价比高、易于开发、社区支持强大等特点,在工业控制、消费电子、智能家居、物联网等领域有着广泛的应用。

时钟系统

STM32F103的时钟可分为内部时钟和外部时钟两类:

-

内部时钟(HSI/LSI):

-

优点:无需外接元件,成本低,启动快,抗干扰强。

-

缺点:精度低(RC振荡器),适合非精确场景(如看门狗、应急备用)。

-

-

外部时钟(HSE/LSE):

-

优点:精度高(晶体振荡),稳定性好,适合高速通信、实时计时(如USB、RTC)。

-

缺点:需外接晶体,增加硬件成本,启动时间略长。

-

不同时钟配置和采样率下的侧信道分析比较

HSI + 48M Samples/S异步采样

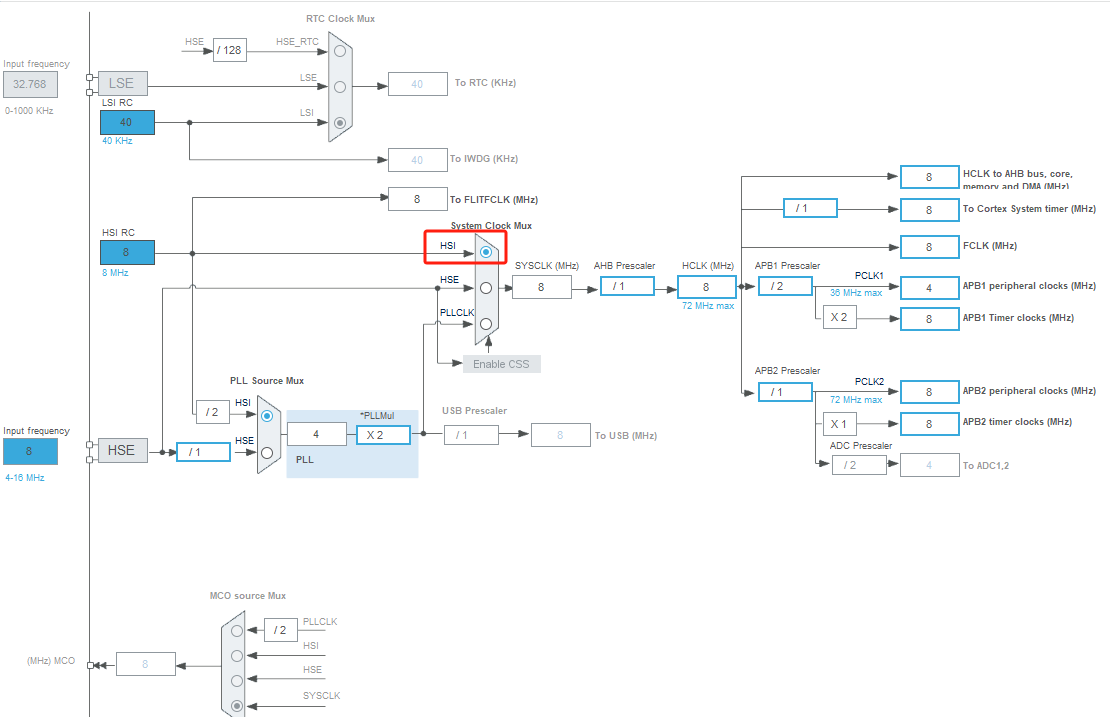

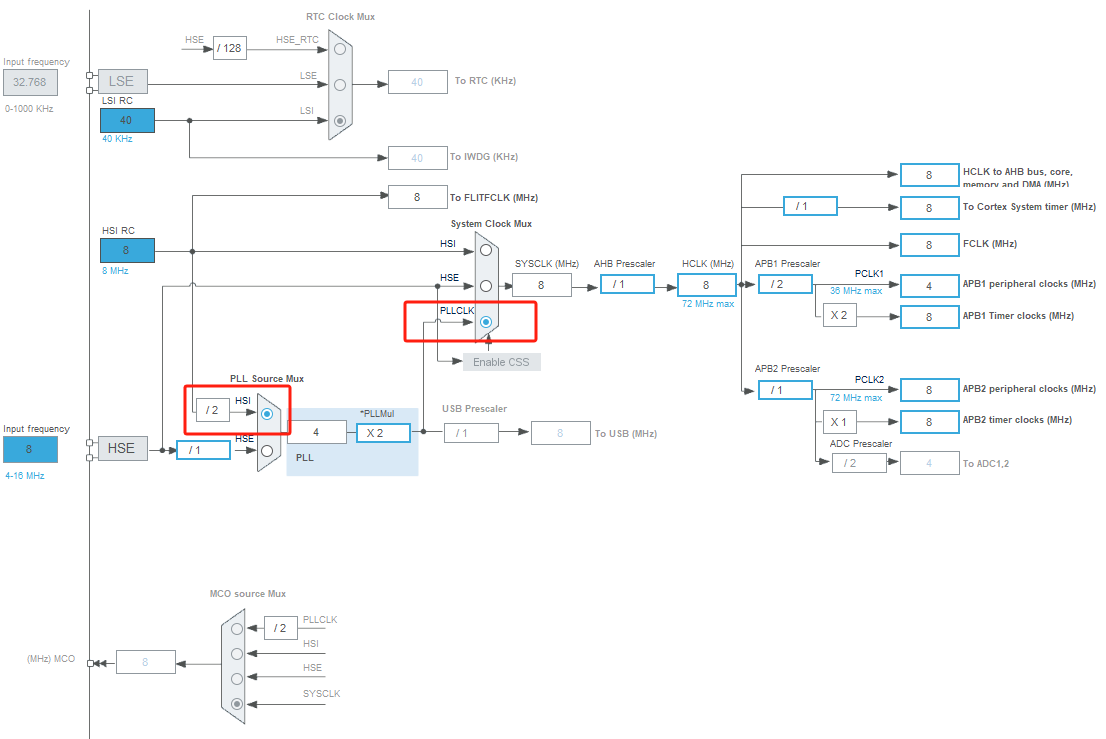

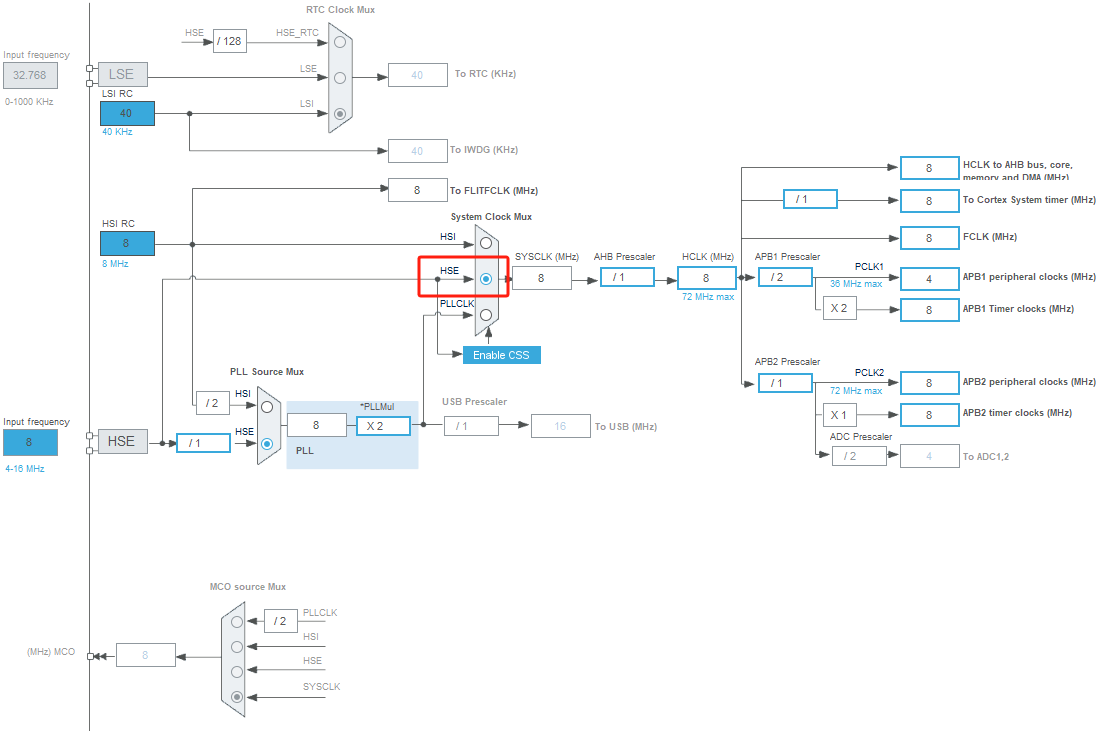

芯片系统时钟采用内部HSI时钟源,SYSCLK配置为8MHz,采样率设置为48M Samples/S(SYSCLK的整数倍),芯片内部时钟配置如下图所示。

上图时钟采用内部8MHz的HSI RC时钟源,经过System Clock Mux后,得到的SYSCLK最终为8MHz。

此处需理解HSI、HSE、PLL等时钟配置,在不同时钟模式下,侧信道信号采集结果和功耗分析结果会存在较大差别。

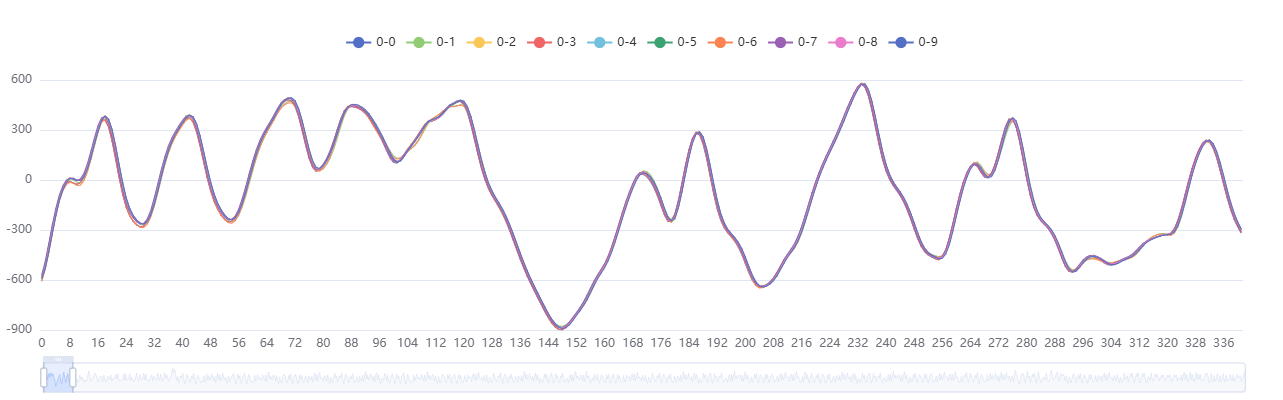

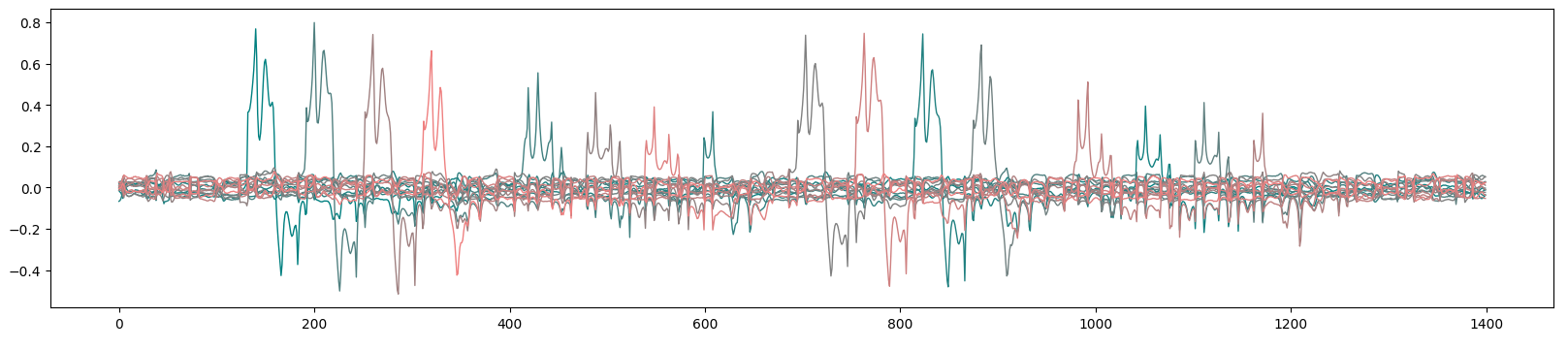

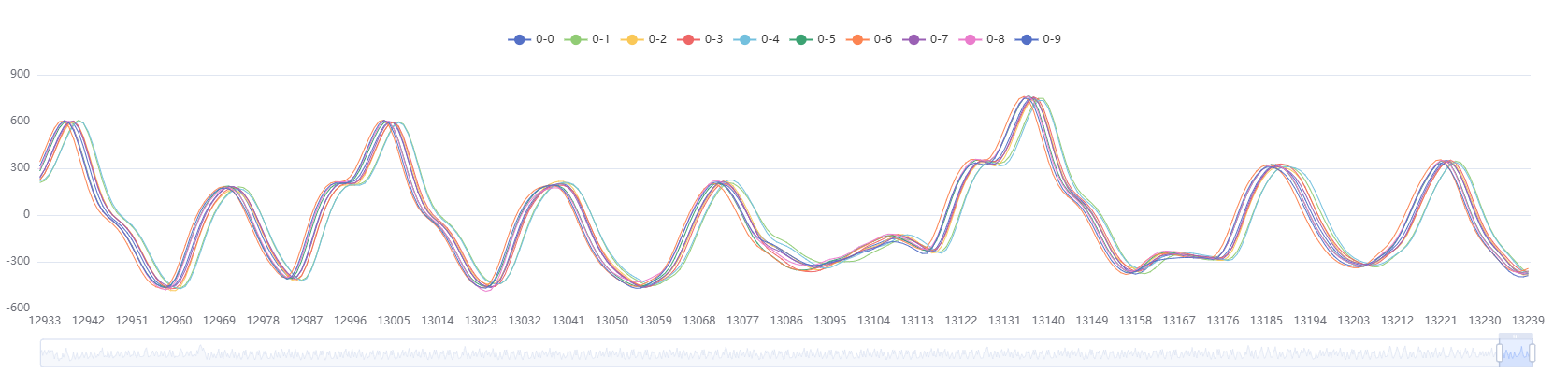

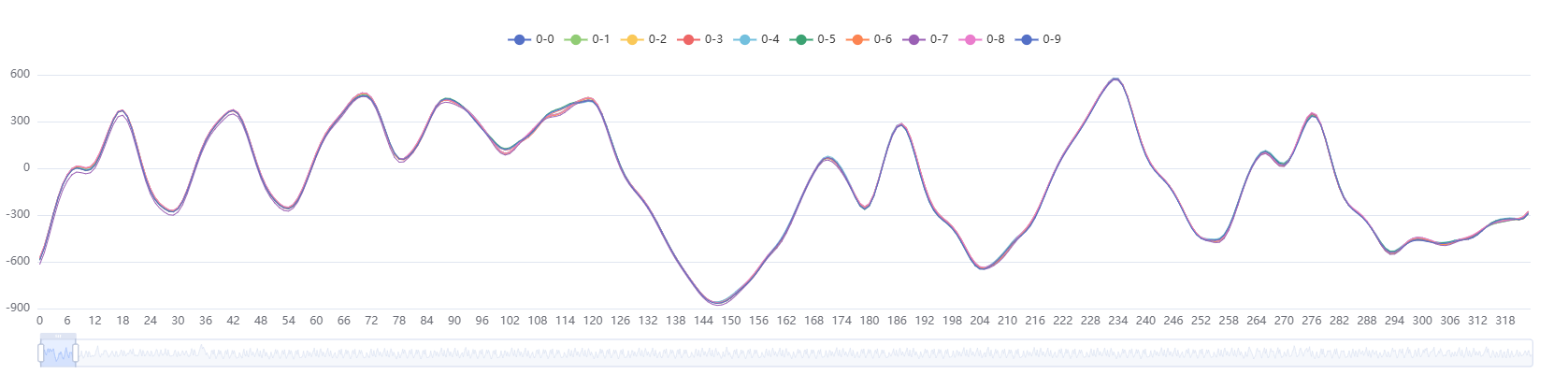

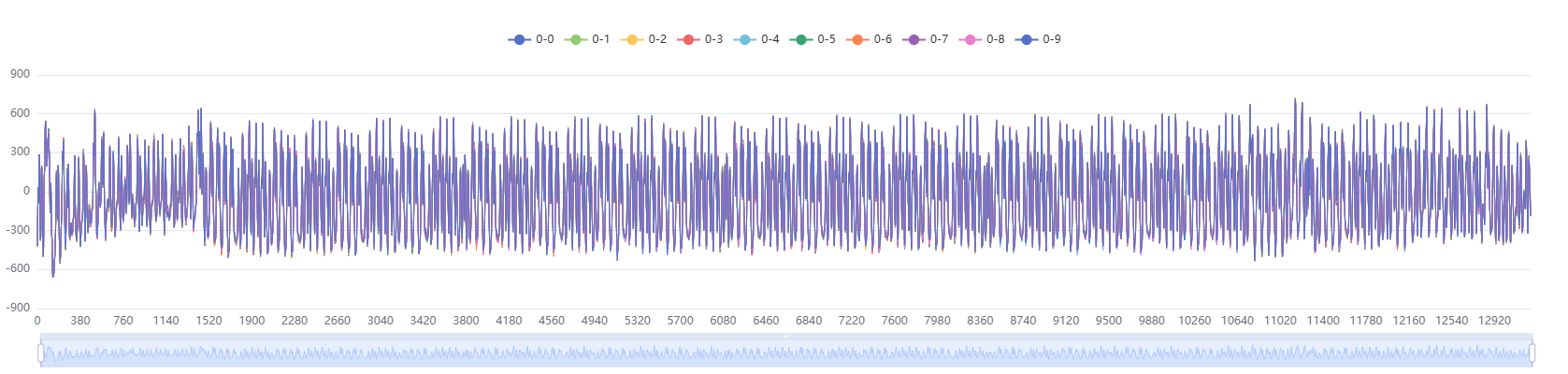

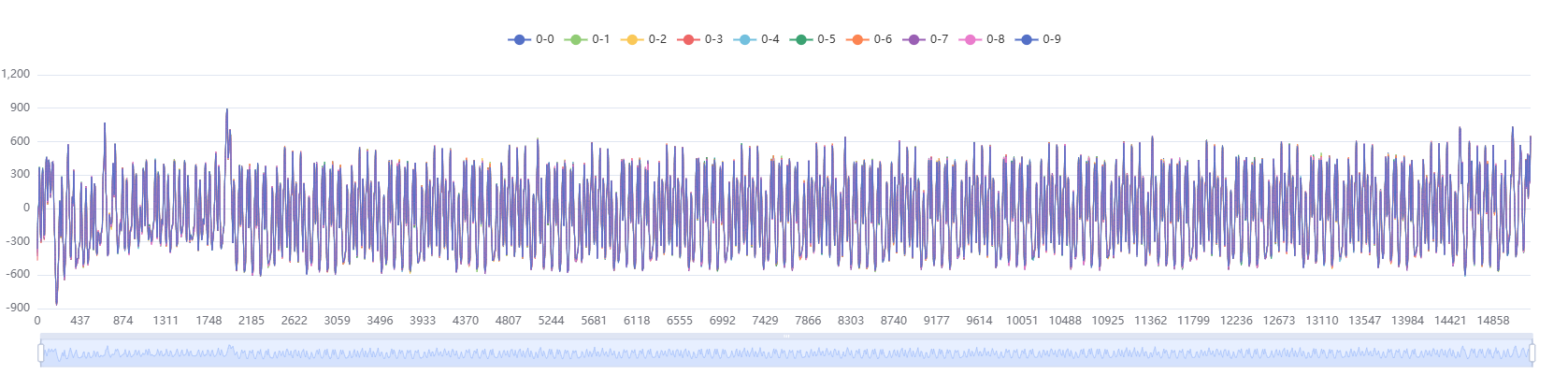

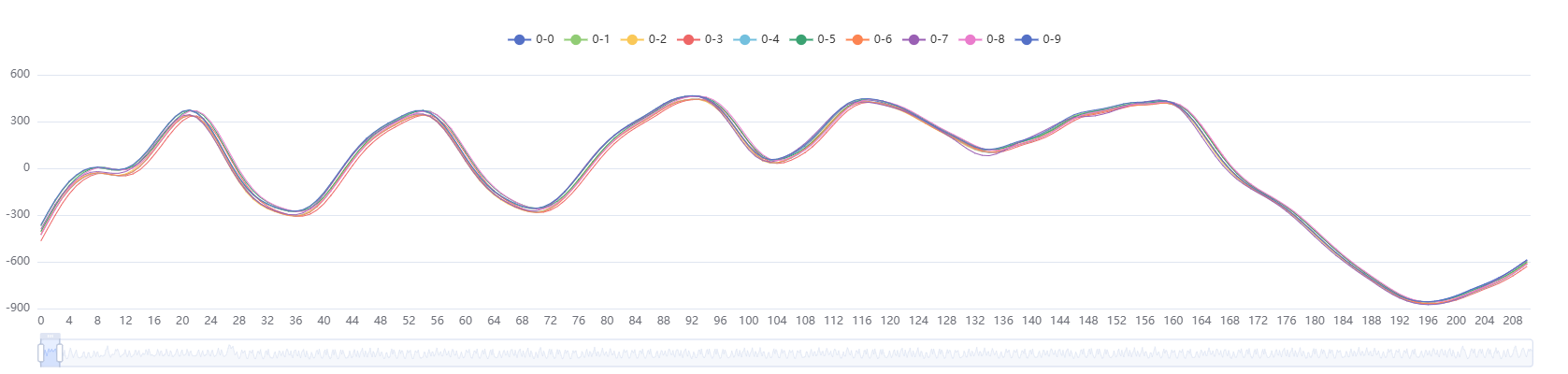

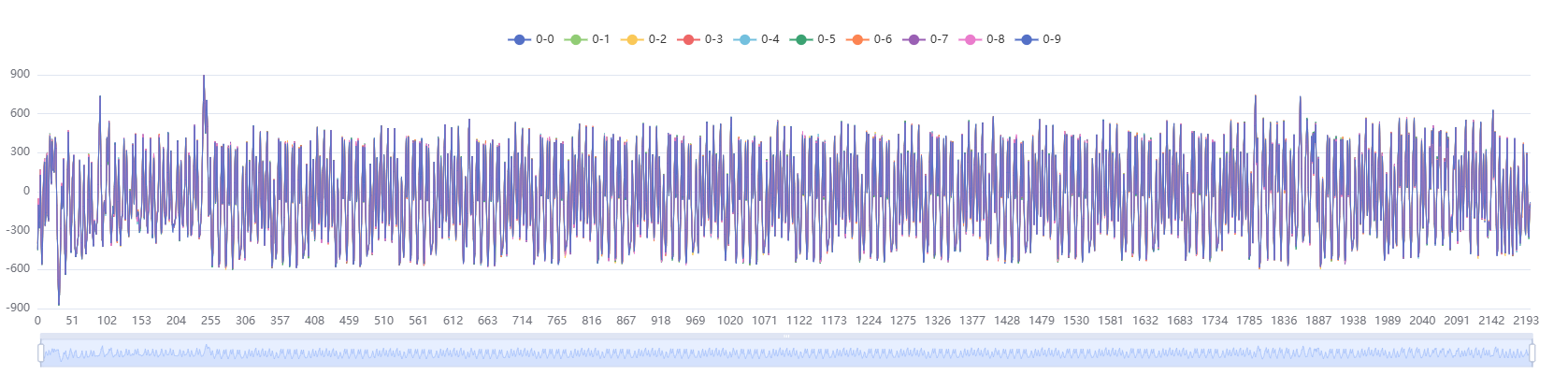

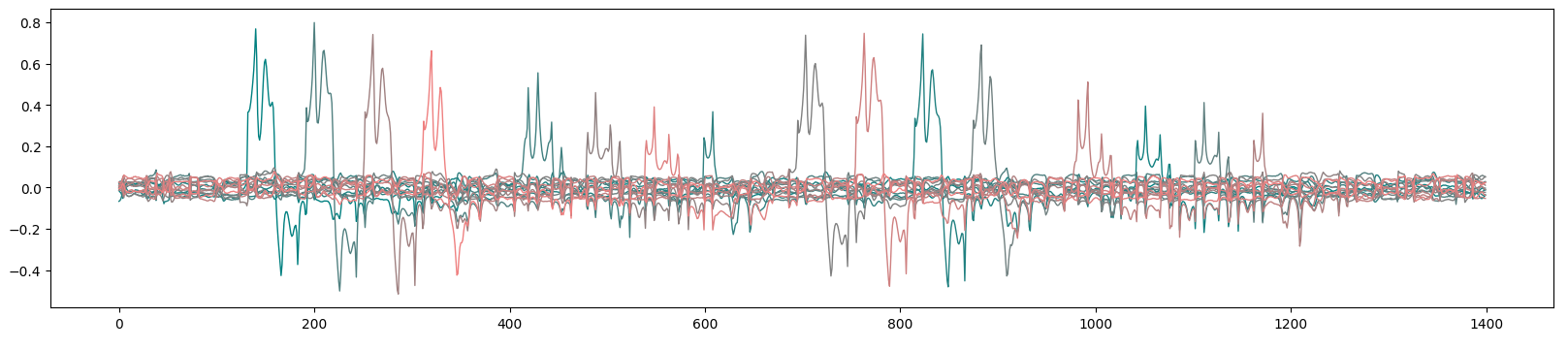

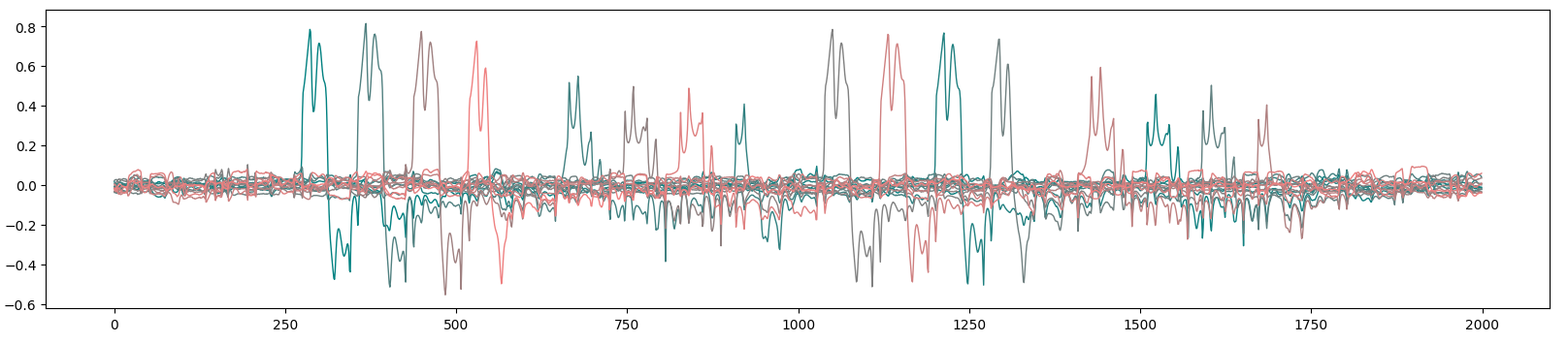

采集到的AES软件实现功耗曲线如下图所示,显示前10条曲线,从图中可以清晰看到16轮加密操作的曲线特征。

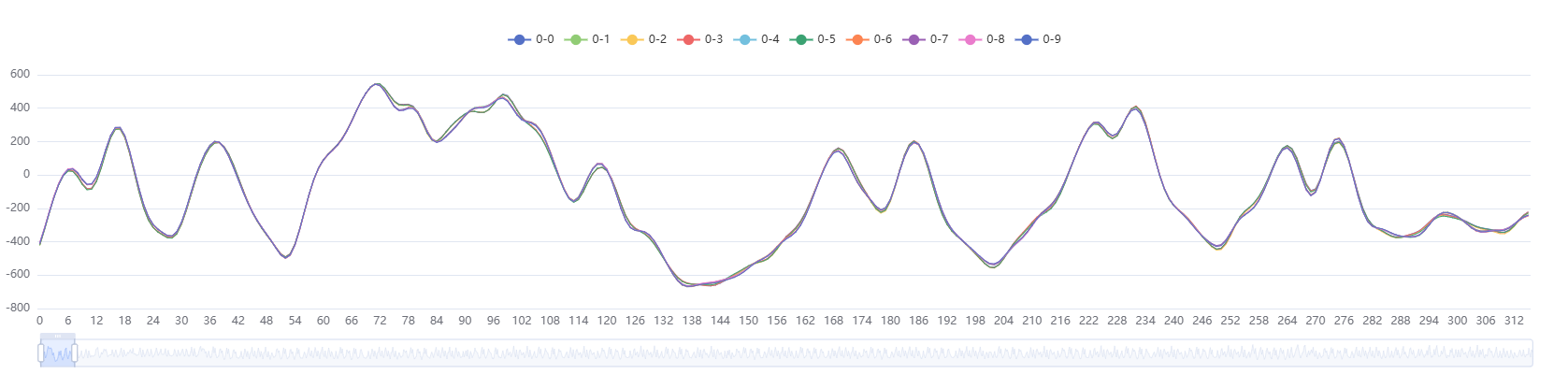

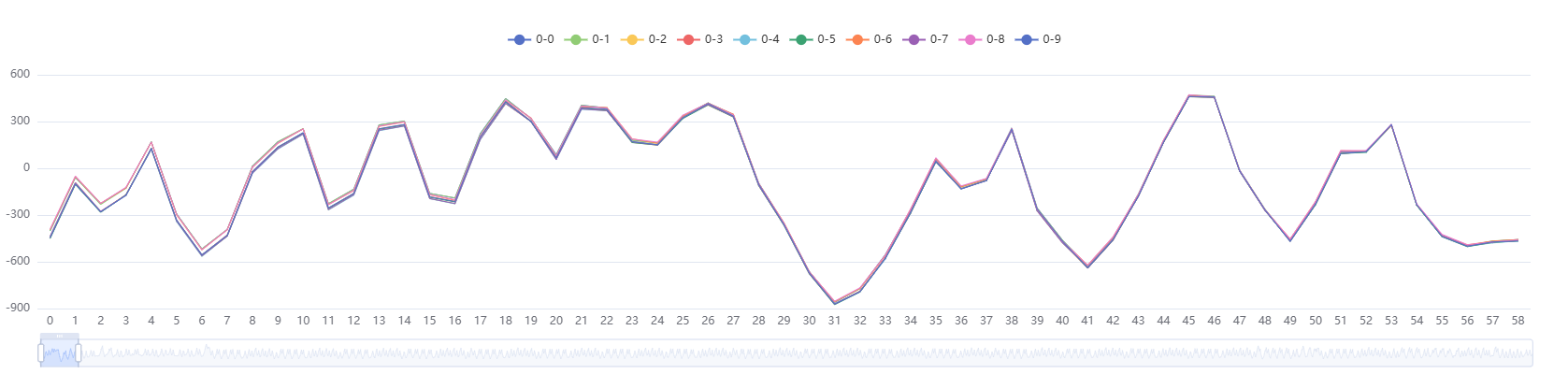

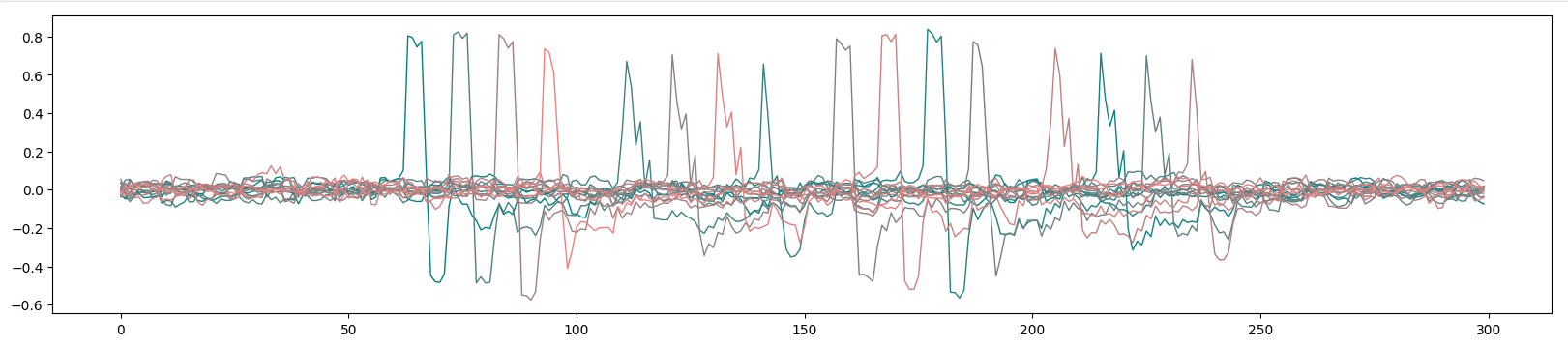

对最开始部分的曲线放大,如下图所示,可以看到曲线重合较好。

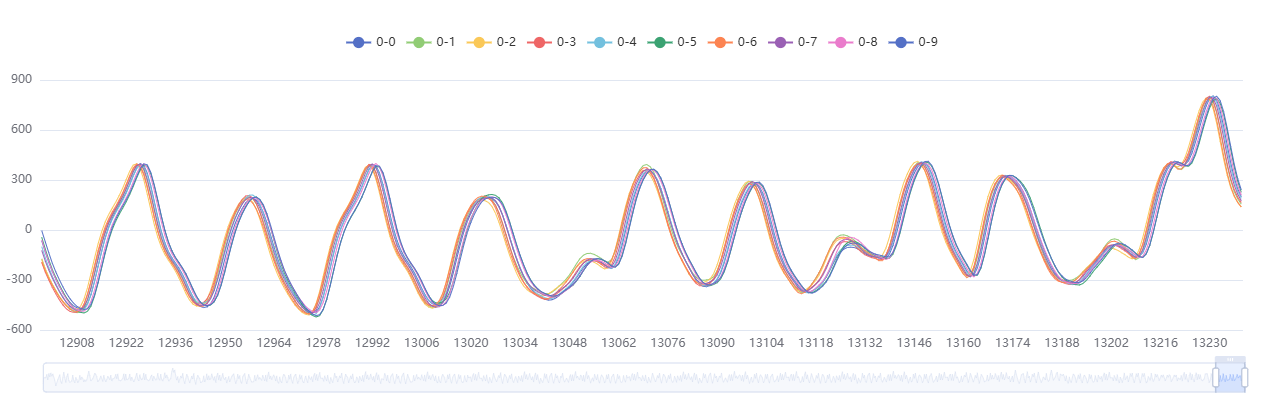

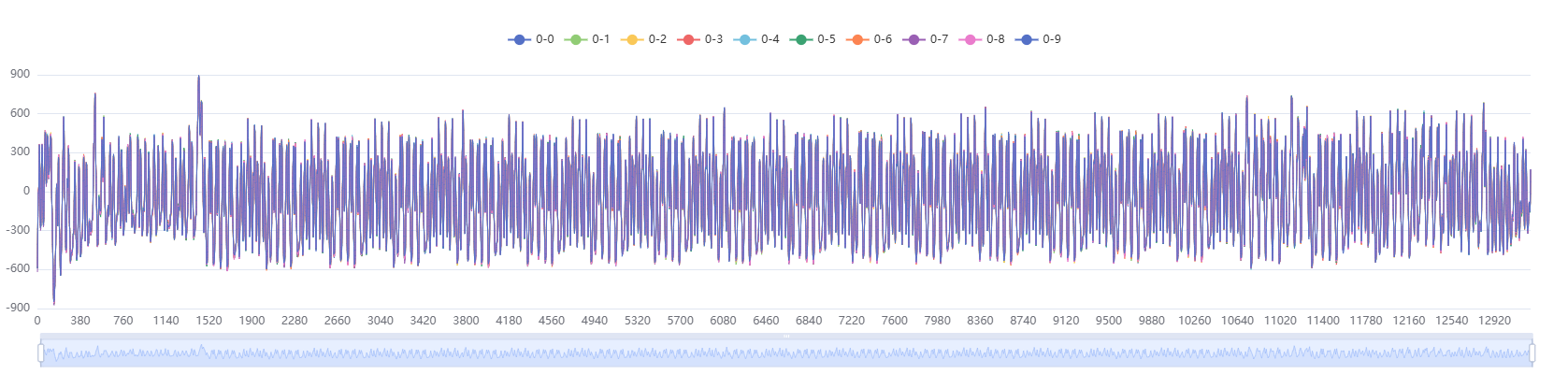

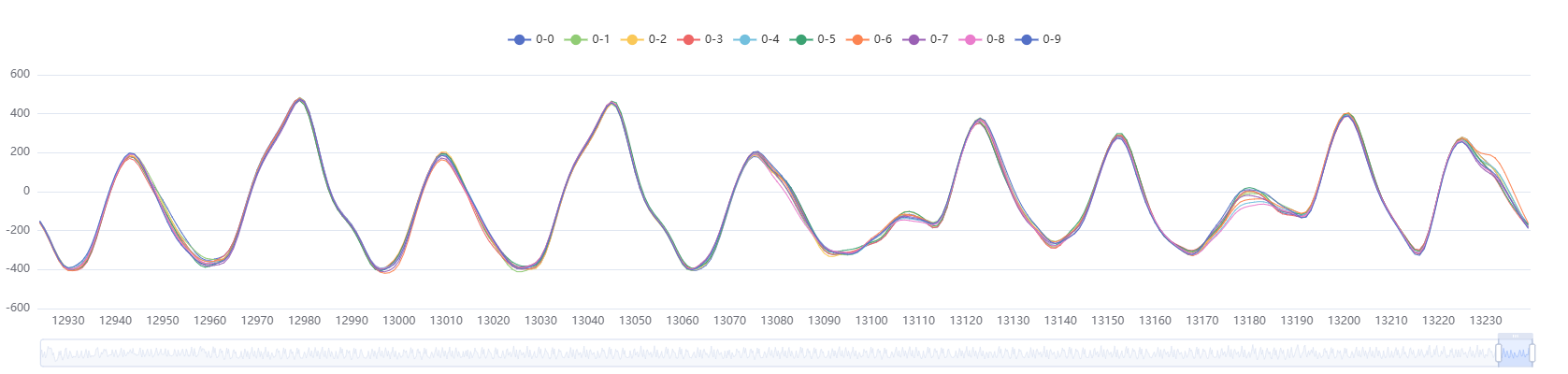

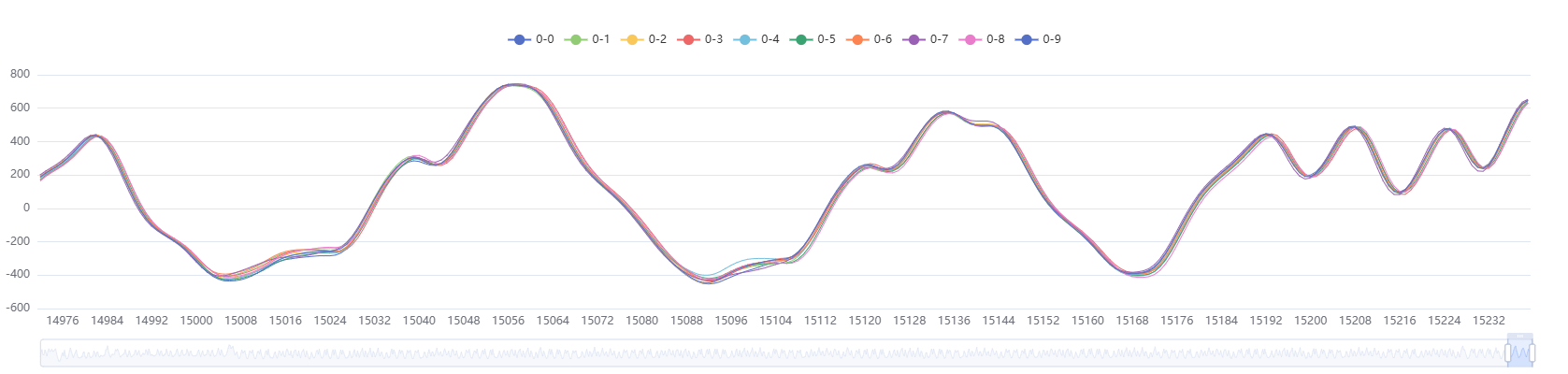

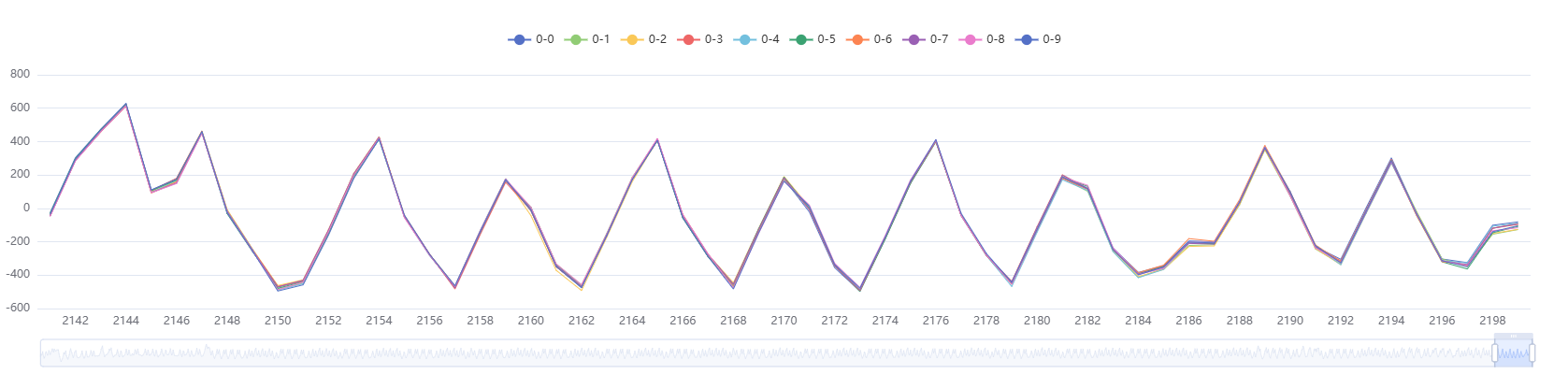

将放大区间移到曲线最后,如下图所示,可以看到各条曲线重合性变差。

内部高速时钟HSI产生的时钟不稳定,导致曲线在时间尺度上对齐性变差。

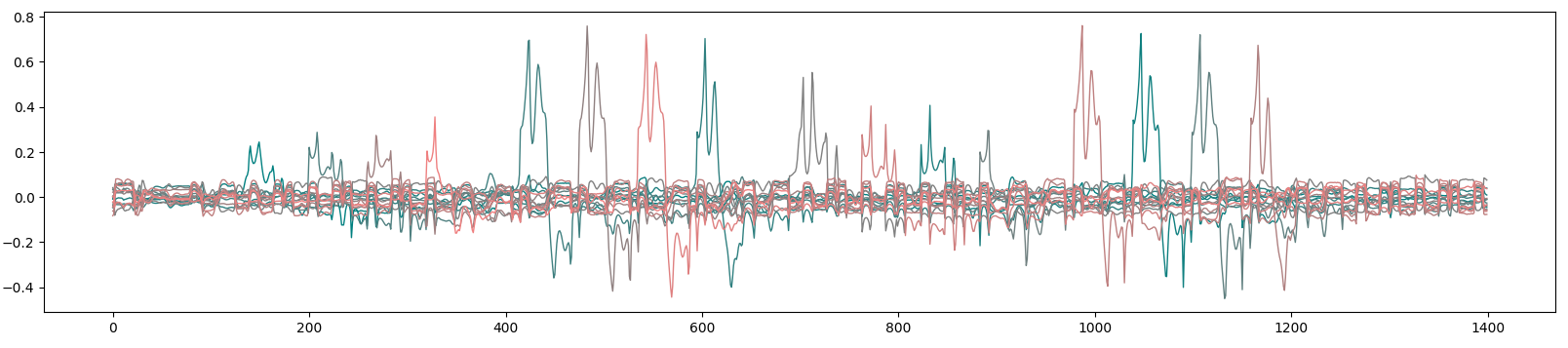

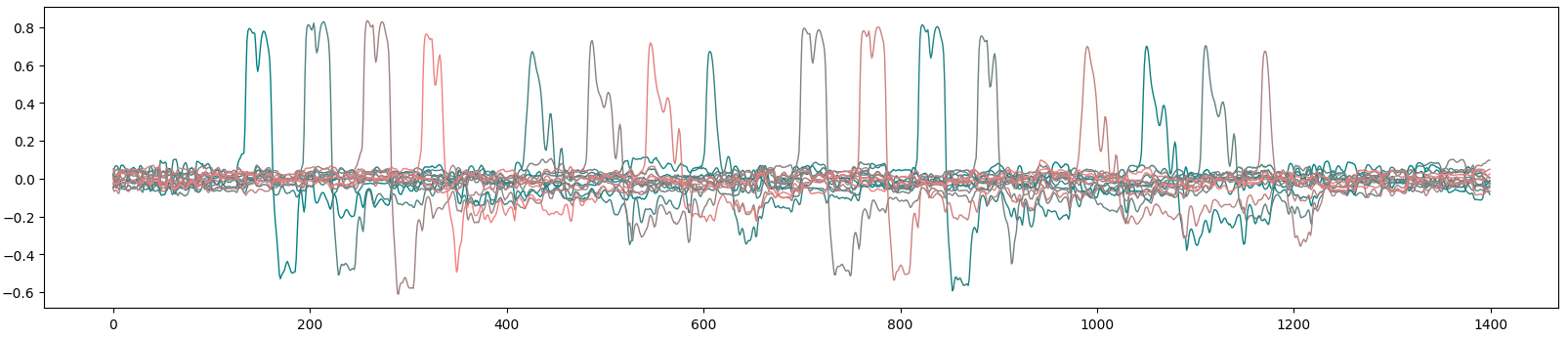

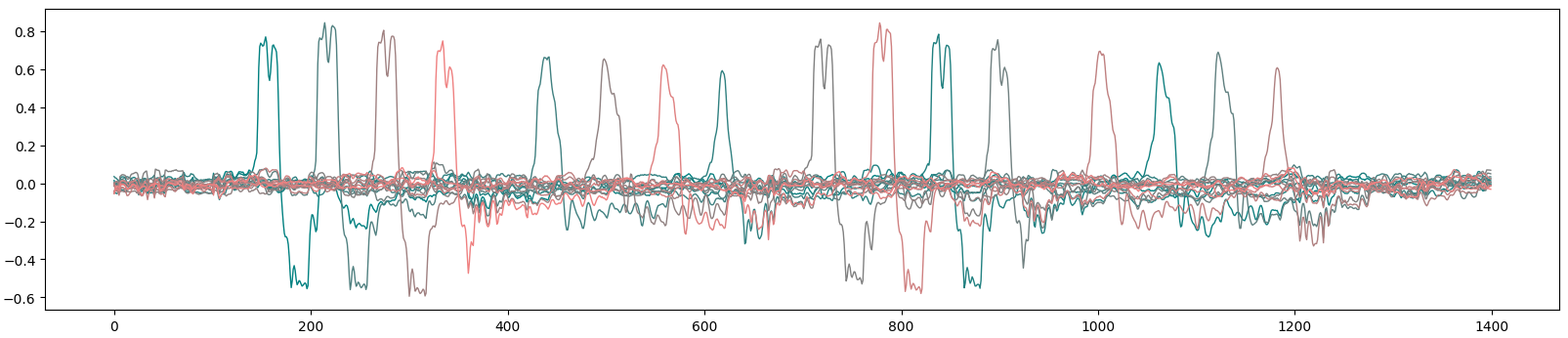

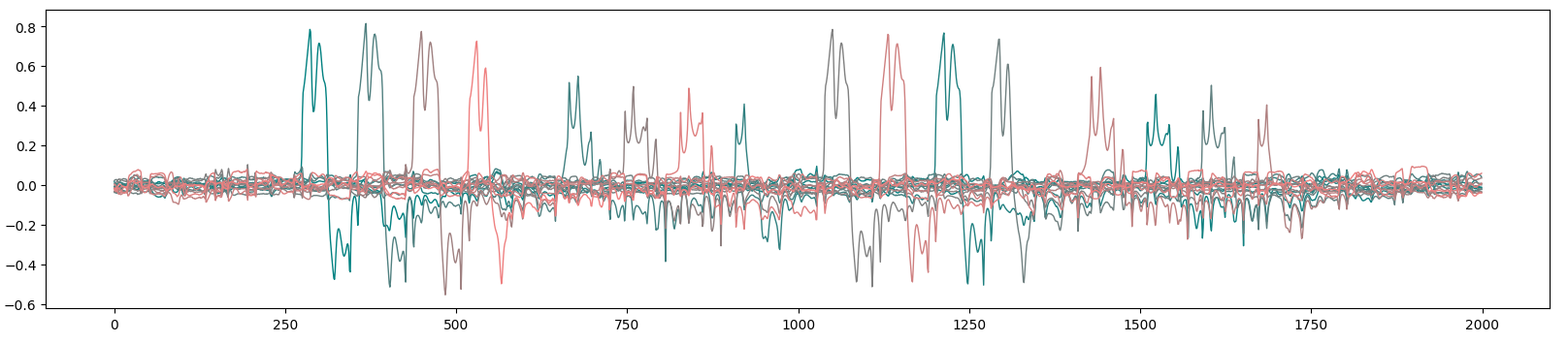

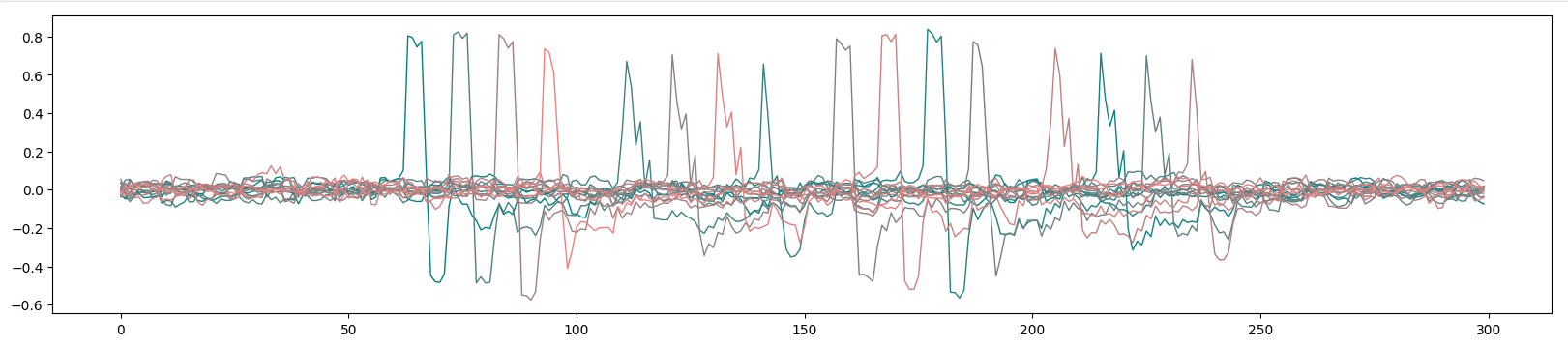

对1000条曲线的第一轮S盒输出位置做CPA分析,分析结果如下图所示。

从图中可以看出,密钥使用存在2种模式,密钥信息泄露最大的位置相关系数接近0.8。

HSI + PLL + 48M Samples/S异步采样

芯片系统时钟采用内部HSI+PLL时钟源,SYSCLK配置为8MHz,采样率设置为48M Samples/S(SYSCLK的整数倍),芯片内部时钟配置如下图所示。

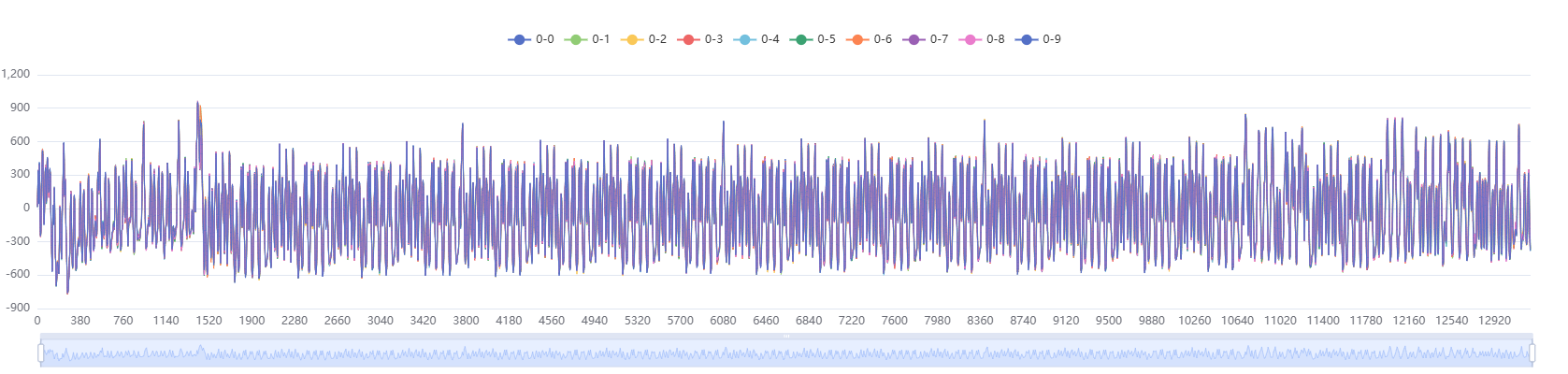

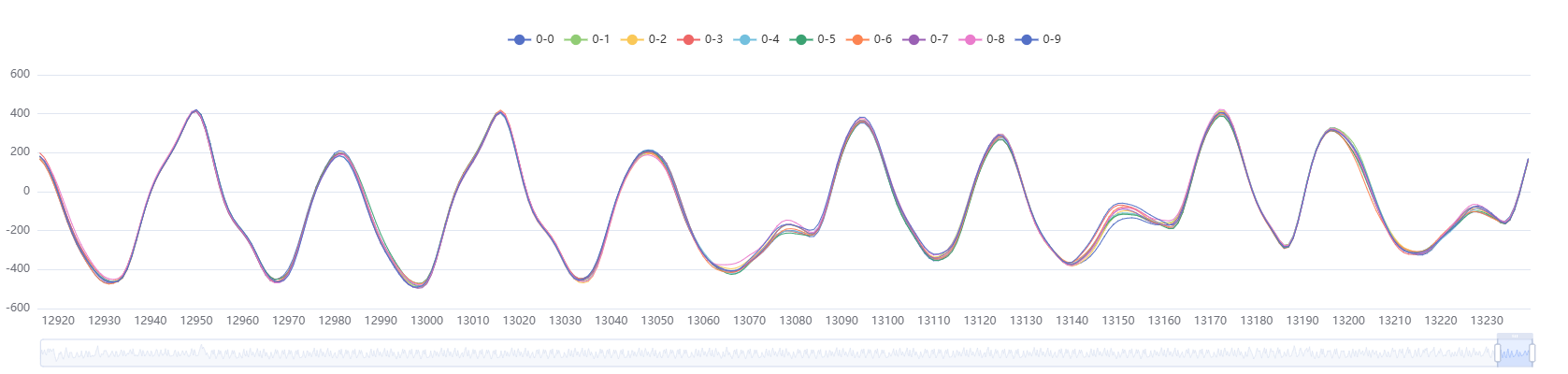

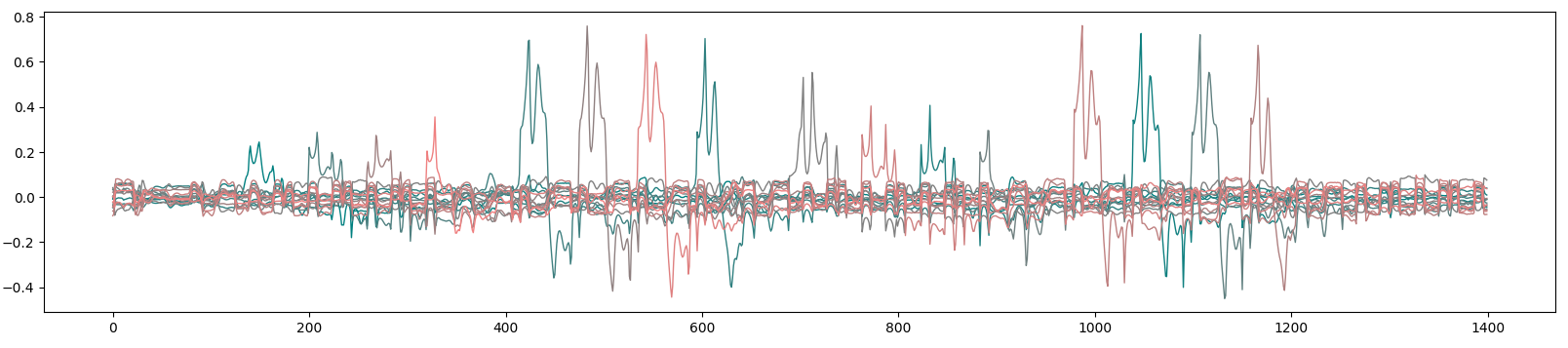

采集到的AES软件实现功耗曲线如下图所示,显示前10条曲线,从图中可以清晰看到16轮加密操作的曲线特征。

对最开始部分的曲线放大,如下图所示,可以看到曲线重合较好。

将放大区间移到曲线最后,如下图所示,可以看到各条曲线重合性变差。

内部高速时钟HSI配合内部PLL产生的时钟不稳定,导致曲线在时间尺度上对齐性变差。

对1000条曲线的第一轮S盒输出位置做CPA分析,分析结果如下图所示。

从图中可以看出,密钥使用存在2种模式,密钥信息泄露最大的位置相关系数接近0.8。同仅HSI模式相比,每4个字节的信息泄露变化产生明显差别。

HSE + 48M Samples/S同步采样

芯片系统时钟采用内部HSE时钟源,SYSCLK配置为8MHz,采样率设置为48M Samples/S(SYSCLK的整数倍),芯片内部时钟配置如下图所示。

使用HSE外部时钟,需开启Cracker-S1对外输出时钟功能。

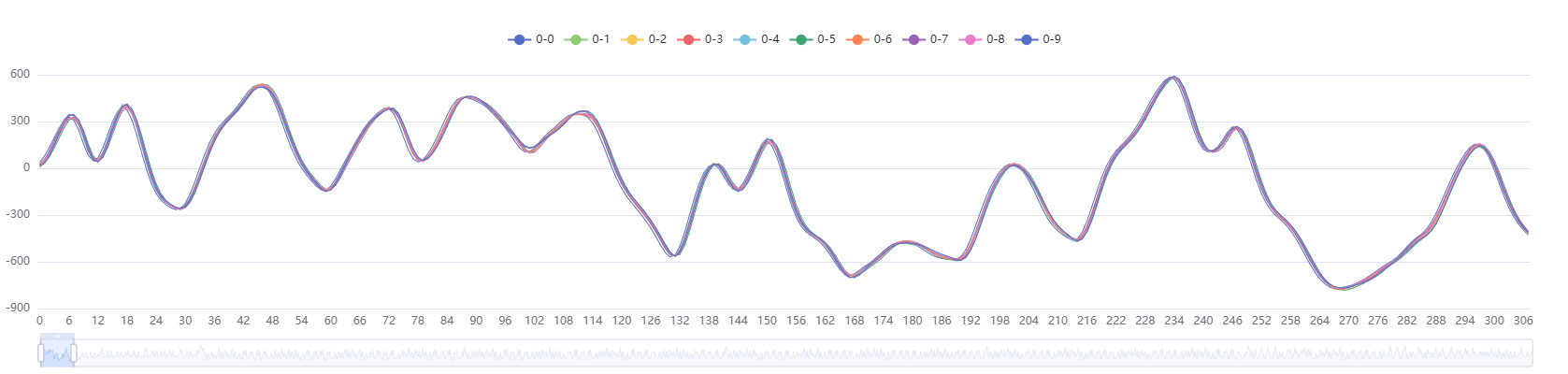

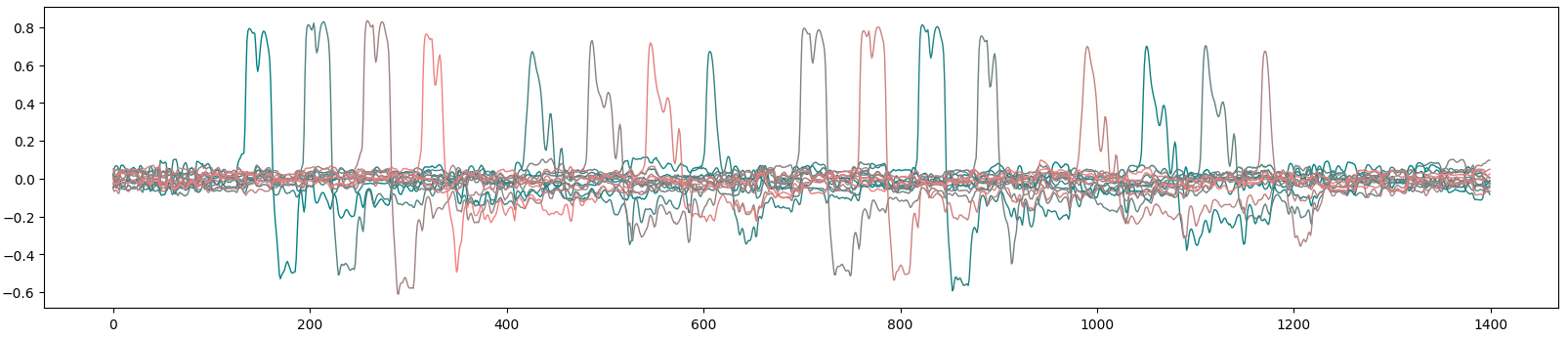

采集到的AES软件实现功耗曲线如下图所示,显示前10条曲线,从图中可以清晰看到16轮加密操作的曲线特征。

对最开始部分的曲线放大,如下图所示,可以看到曲线重合较好。

将放大区间移到曲线最后,如下图所示,可以看到各条曲线重合性未变差。

对1000条曲线的第一轮S盒输出位置做CPA分析,分析结果如下图所示。

从图中可以看出,密钥使用存在2种模式,密钥信息泄露最大的位置相关系数超过0.8。同两种HSI模式相比,信息泄露明显变强。

STM32外部时钟和ADC采样时钟同源,保证了每个周期都可以精确的采集到6个数据(48M/8M),大大提高了侧信道分析成功率。

HSE + PLL + 48M Samples/S同步采样

芯片系统时钟采用内部HSE+PLL时钟源,SYSCLK配置为8MHz,采样率设置为48M Samples/S(SYSCLK的整数倍),芯片内部时钟配置如下图所示。

使用HSE外部时钟,需开启Cracker-S1对外输出时钟功能。

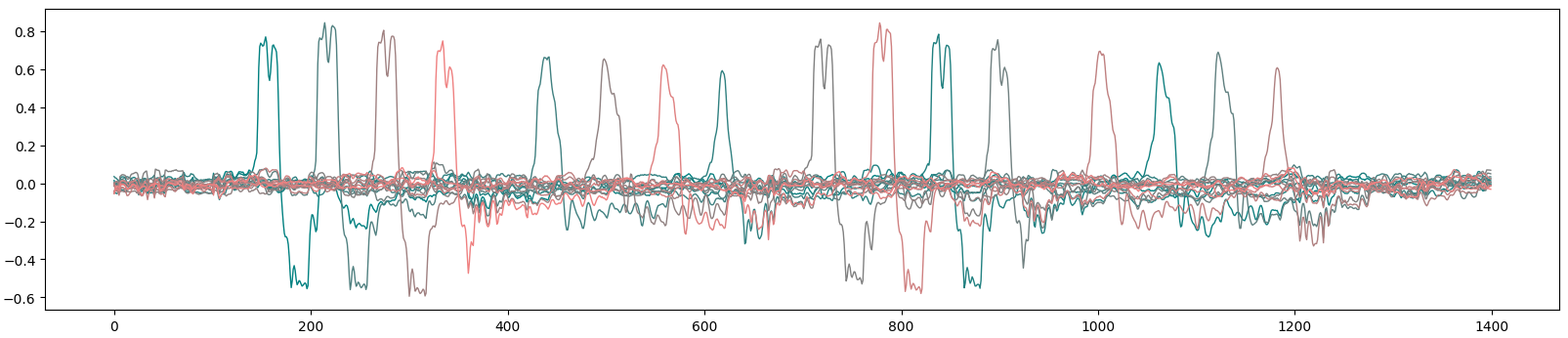

采集到的AES软件实现功耗曲线如下图所示,显示前10条曲线,从图中可以清晰看到16轮加密操作的曲线特征。

对最开始部分的曲线放大,如下图所示,可以看到曲线重合较好。

将放大区间移到曲线最后,如下图所示,可以看到各条曲线重合较好。

对1000条曲线的第一轮S盒输出位置做CPA分析,分析结果如下图所示。

从图中可以看出,密钥使用存在2种模式,密钥信息泄露最大的位置相关系数超过0.8。同两种HSI模式相比,信息泄露明显变强。

HSE + 65M Samples/S异步采样

本次测试仍采用外部8MHz时钟,采样率提高到65M Samples/S,采样率提高,但不是时钟频率的整数倍。

采集到的AES软件实现功耗曲线如下图所��示,显示前10条曲线,从图中可以清晰看到16轮加密操作的曲线特征。

对最开始部分的曲线放大,如下图所示,可以看到曲线重合性变差。

将放大区间移到曲线最后,如下图所示,可以看到曲线重合性变差。

对1000条曲线的第一轮S盒输出位置做CPA分析,分析结果如下图所示。

从图中可以看出,密钥使用存在2种模式,密钥信息泄露最大的位置相关系数超过0.8。与同步采样相比,虽然采样率提高,但密钥相关性有所降低。

HSE + 8M Samples/S异步采样

本次测试仍采用外部8MHz时钟,采样率降低到8M Samples/S,采样率降低,与芯片时钟频率相同。

采集到的AES软件实现功耗曲线如下图所示,显示前10条曲线,从图中可以清晰看到16轮加密操作的曲线特征。

对最开始部分的曲线放大,如下图所示,可以看到曲线重合较好。

将放大区间移到曲线最后,如下图所示,可以看到各条曲线重合较好。

对1000条曲线的第一轮S盒输出位置做CPA分析,分析结果如下图所示。

从图中可以看出,密钥使用存在2种模式,密钥信息泄露最大的位置相关系数超过0.8。

不同模式侧信道分析效果对比

| 模式 | 分析结果 |

|---|---|

| HSI + 48M异步采样 |  |

| HSI + PLL + 48M异步采样 |  |

| HSE + 48M同步采样 |  |

| HSE + PLL + 48M同步采样 |  |

| HSE + 65M异步采样 |  |

| HSE + 8M同步采样 |  |

从分析结果看,采用外部时钟+同步采样方式效果最好,如想节省计算时间,可采用芯片时钟同频、同步采样方式。

相关脚本和数据文件可在 https://pan.baidu.com/s/1jLVV_ViPUspbqgIOSOFyOQ?pwd=utyy 进行下载。